I have a AsRock X570 Taichi motherboard with a AMD 3900XT. There are:

3 x PCIE 4.0 x 16 slots (PCIE1/PCIE3PCI5)

[single at x 16 (PCIE1)

dual at x 8 (PCIE1) / x8(PCIE3)

triple at x8(PCIE1) / x8(PCIE3) / x4 (PCIE5)]

2 x PCIE 4.0 x 1 slots (PCIE2, PCIE4)

and for storage:

1 x Hyper M.2 socket (M2_1) supports SATA and M.2 PCI Express module up to Gen4x4

1 x Hyper M.2 socket (M2_2) supports SATA and M.2 PCI Express module up to Gen4x4

1 x Hyper M.2 socket (M2_3) supports SATA and M.2 PCI Express module up to Gen4x4

*If M2_3 is occupied, PCIE5 slot will be disabled

I get the * part of it. If M2_3 is used then PCIE5 no longer works. Basically, M2_3 takes up all the traffic lanes. If I am understanding this correctly, the M.2 sockets operate off the PCIE lanes thus if I have all three slots occupied, it's possible that storage devices could be taking up to 12 PCIE traffic lanes...?

If I occupy ONLY PCIE1 then that device has access to all 16 PCIE lanes....which could potentially be throttled down to just x4 lanes if all three M.2 sockets that up their max x12 lanes...?

If I occupy two PCIE slots (PCIE1 and PCIE3) then both devices get only x8 lanes...which could potentially be throttled down by the M.2 sockets...?

Here's where I'm losing it:

If I take out M.2_3 - giving me access to PCIE5 - and I occupy PCIE1, PCIE3 and PCI5 then both devices on PCIE1 and PCI3 get x8 lanes each but PCIE5 only gets x4 lanes. <- That's more than x16 lanes...? Or are they only allowed these many lanes MAXIMUM?

Let's say I somehow was able to physically occupy all the PCIE slots (PCIE1, PCIE2, PCIE3, PCIE4 and PCIE5). PCIE1 and PCI3 get x8 lanes each but PCIE5 only gets x4 lanes. PCI2 and PCI4 each get 1 lane each. <- again more than 16 lanes. Or is this the MAX number of lanes they are allowed? So if PCIE1 has heavy traffic and there are no other loads, PCIE1 gets a MAX of x8 lanes...?

EDIT:

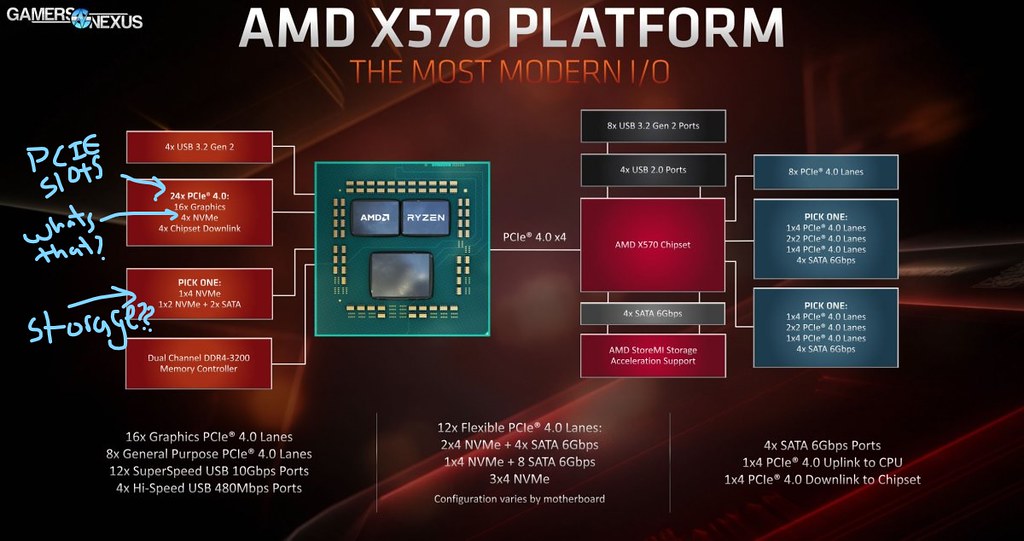

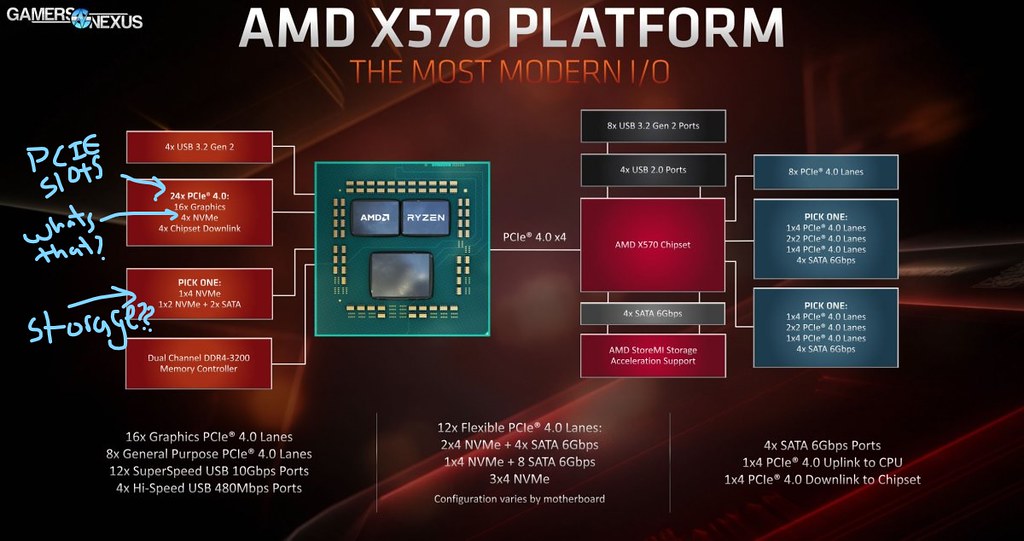

Just found a X570 block diagram but I'm still confused...there are x20 PCIE lanes?

3 x PCIE 4.0 x 16 slots (PCIE1/PCIE3PCI5)

[single at x 16 (PCIE1)

dual at x 8 (PCIE1) / x8(PCIE3)

triple at x8(PCIE1) / x8(PCIE3) / x4 (PCIE5)]

2 x PCIE 4.0 x 1 slots (PCIE2, PCIE4)

and for storage:

1 x Hyper M.2 socket (M2_1) supports SATA and M.2 PCI Express module up to Gen4x4

1 x Hyper M.2 socket (M2_2) supports SATA and M.2 PCI Express module up to Gen4x4

1 x Hyper M.2 socket (M2_3) supports SATA and M.2 PCI Express module up to Gen4x4

*If M2_3 is occupied, PCIE5 slot will be disabled

I get the * part of it. If M2_3 is used then PCIE5 no longer works. Basically, M2_3 takes up all the traffic lanes. If I am understanding this correctly, the M.2 sockets operate off the PCIE lanes thus if I have all three slots occupied, it's possible that storage devices could be taking up to 12 PCIE traffic lanes...?

If I occupy ONLY PCIE1 then that device has access to all 16 PCIE lanes....which could potentially be throttled down to just x4 lanes if all three M.2 sockets that up their max x12 lanes...?

If I occupy two PCIE slots (PCIE1 and PCIE3) then both devices get only x8 lanes...which could potentially be throttled down by the M.2 sockets...?

Here's where I'm losing it:

If I take out M.2_3 - giving me access to PCIE5 - and I occupy PCIE1, PCIE3 and PCI5 then both devices on PCIE1 and PCI3 get x8 lanes each but PCIE5 only gets x4 lanes. <- That's more than x16 lanes...? Or are they only allowed these many lanes MAXIMUM?

Let's say I somehow was able to physically occupy all the PCIE slots (PCIE1, PCIE2, PCIE3, PCIE4 and PCIE5). PCIE1 and PCI3 get x8 lanes each but PCIE5 only gets x4 lanes. PCI2 and PCI4 each get 1 lane each. <- again more than 16 lanes. Or is this the MAX number of lanes they are allowed? So if PCIE1 has heavy traffic and there are no other loads, PCIE1 gets a MAX of x8 lanes...?

EDIT:

Just found a X570 block diagram but I'm still confused...there are x20 PCIE lanes?