The information to support or refute your ideas is out there,

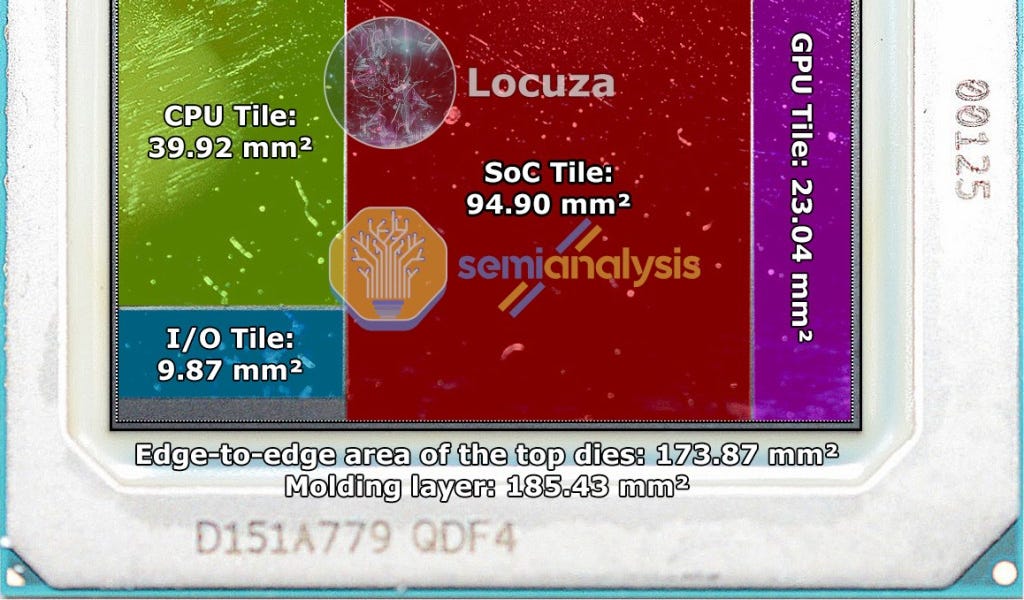

if you're willing to look for it. Locuza did a detailed die-shot analysis of Alder Lake, here:

First, Golden Cove core is estimated at 7.53 mm^2 (or 5.88 mm^2 without L2 cache). Then, the article goes on to speculate that:

"On the other hand, we could also remove a bit of area for Golden Cove, since Intel really doesn’t want the AVX512 capabilities to be exposed, which increase the size of the register files and execution units. Without considering core floorplan challenges, you may in theory gain about 1 to 2 mm²."

I believe that was referring to the

cumulative area for the

whole die, because the analysis later estimates the size of Golden Cove's

entire VFP unit at 0.986 mm^2! So, Locuza estimates dropping AVX-512 would only slim it down to 0.736 mm^2

at best!

The article then goes on to compare Golden Cove to Gracemont, estimating a the latter's core at 1.63 mm^2 (including everything but L2). This puts the

entire Golden Cove VFP unit at 62% of a Gracemont core. In other words, deleting AVX-512 from Golden Cove would shrink it by a mere fraction of the area of

one Gracemont core. That's further confirmation that any contribution AVX-512 makes to the area of Golden Cove is only making a minor dent in the differential between their respective areas.

So, the simple answer is:

no. AVX-512 isn't keeping Golden Cove from being "WAY more space efficient". We can't really say much about power efficiency, but I believe the upper 256-bits of AVX-512 registers remain inactive, as long as a program never touches them.

www.realworldtech.com

A lot has been published by Intel and others about Gracemont. If you

truly want to understand how it's so much more efficient than Golden Cove, the answers are out there and not hard to find. I already posted a link to Chips & Cheese and here's what Anandtech published from Intel's Architecture Day:

Zen 4's VFP implementation is the same width as Golden Cove's. It's just sub-divided into more, narrower ports. That doesn't help AMD with power-efficiency. The main efficiency benefit for AMD is that they waited to implement it on TSMC N5.

The main difference is that Intel has double the FMA ports, whereas Zen 4 can only schedule Adds, in those slots. I'm reasonably certain AMD and Intel reuse the same datapaths and ALUs for both AVX and AVX-512. If not, then that's

even more reason to think it's not hurting Golden Cove's efficiency.

AMD Implemented all of the same AVX-512 ISA extensions as Ice Lake. The only additional instructions implemented by Golden Cove are for fp16 support.

en.wikipedia.org

Now, I've just spent about an hour of my time explaining what you could've looked up, yourself. In the future,

please check your own facts, instead of making poorly-informed statements and relying on others to catch when you're demonstrably wrong.