I am a bit lost on whether Raphael will be an APU-only design or Zen3 style chiplets (or both again).

I would still assume that AMD just can't/won't do twenty different die variants, since they're not Intel.

Their APU chips covered an awful lot of ground rather well with Cezanne, I've played with it as 5800U at 15/28 Watts to a 5700G at 65 Watts and will admit that it's hard to get 2x benefit from my 16-core 5950X with real-life use cases. And for those who really need that, someone will pay EPYCally.

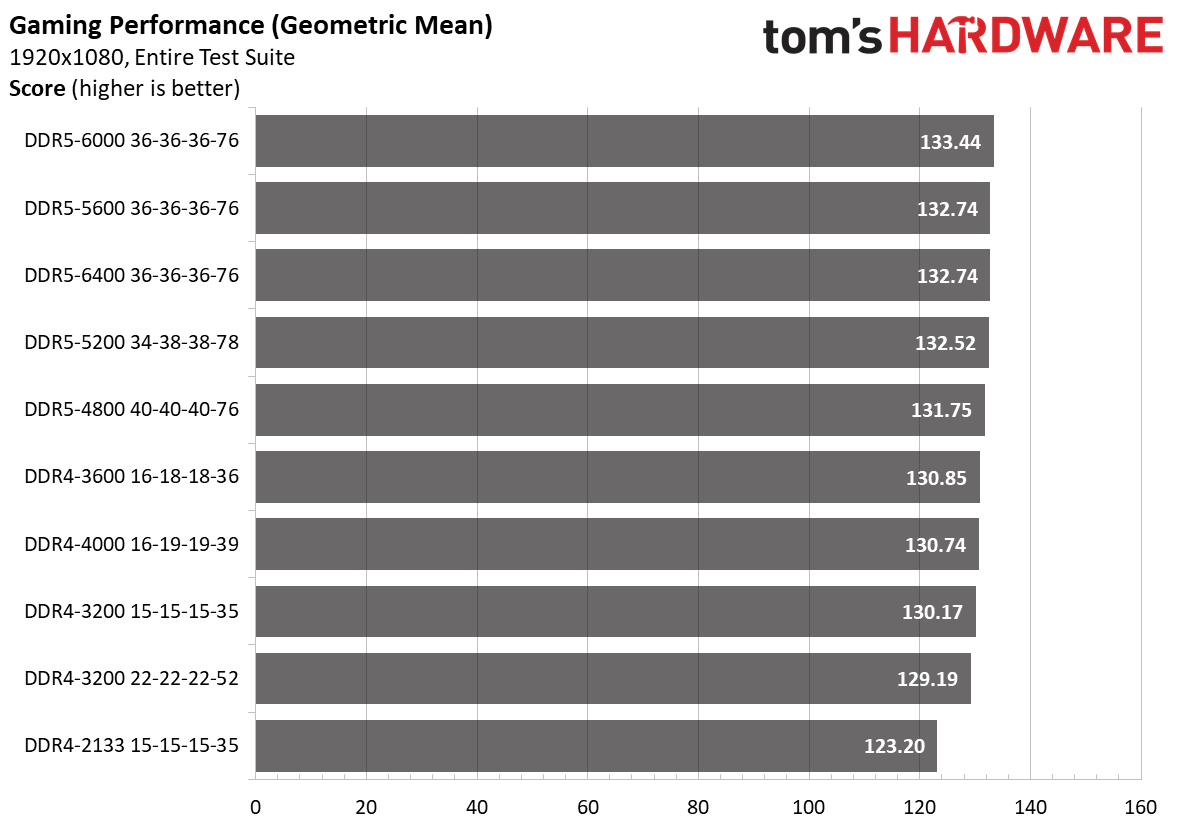

Beyond a certain number of cores your (CPU) code base is less likely to be nicely threaded (or it is already vectored), so memory access patterns from decoupled code become so spread out you'll need more independent channels (assuming AM5 will still be limited to two channels for economy) or much bigger caches (5800X3D) to avoid stalling on RAM access. The bandwidth advantage of DDR5 won't translate to better random access performance.

I'm not sure we'll actually see a 16-core AM5 chip when they could use the area for things that sell in higher volumes. E.g. to put an extra set of DDR5 channels for the iGPU frame buffer there on the die carrier somewhat Apple M1 style while still maintaining two external channels for soldered RAM or DIMMs. That way they could get a total of 4 channels of RAM for iGPU use, while two channels would go off die carrier for normal code/data expandability.

Depending on just how dense/big such DDR5 RAM stacks might be, you might even be able to expand this again Apple style to a dual APU on single die-carrier system, with only one set of external RAM and I/O going off die carrier to maintain the AM5 socket constraints. There is a lot of surface area on the AM5 socket and now some extra Wattage, too. I count on AMD to surprise us with something smart.

Intel has always been far too comfortable throwing in lots of die area without monetization (they never really charged for the iGPU and felt much too comfortable about deactivating cores and blocks) and AMD's kicker with Zen has been to make every transistor count. To include a backward oriented DDR4 RAM interface as a migration compromise is just too much of a waste in transistors and AM5 socket specs when that is designed for long term.

The APU design isn't driven by the desktop, even if it might be driving the vast majority of desktops. It's driven by notebooks and there the power consumption vs. bandwidth optimizations of the new RAM generation, even if that won't be cheapest for a couple of months. And on laptops the DDR5 DIMM price penalty may not be nearly as big, because specialty packages with volume contracts may drive that down. And if the DDR5 bandwidth enables everything 3D you need in FHD on the iGPU, that price bump just won't be felt there.

I too am a PC or desktop guy, but even if the PC was the original technology driver for both ISA servers and notebooks, the split between the two has become so large, the desktop on its own is no longer big enough to justify its own technology, but will have to decide between which of the other two it's build on.

And with 8 cores at 5GHz as the new base line, that's a lot of desktop for notebook tech.