jaymc :

AMD Threadripper Delidded, With a Multi-Core Surprise Under the Hood:

https://www.extremetech.com/computing/253248-amd-threadripper-delidded-multi-core-surprise-hood

Not really a surprise since the instant we knew the size of the CPU (same size than EPYC), and that it was going to use a SP3r2 socket (a derivation of the SP3 socket on EPYC).

jaymc :

I wonder if this is why Epyc is not "available" even now as stated by aldaia..

"While that is true, it means absolutely nothing. I just happen to work on one of the supercomputing centers that got a Skylake-SP supercomputer. The reason why EPYC got none is that EPYC was not yet available (it is not even now) while Skylake-SP has been available to "selected customers" since late last year.

Some HPC specialists consider that EPYC offers serious competition to Intel in HPC."

EPYC has been available for many months, and potential customers tested it. "I already tried Naples, and its outright horrible". This is what a friend said said me many months ago when I asked about details: "Like a lot slower, not scaling, power inefficient, poor RSA features and so on and on?" Note, that we talked about it, when it was not still renamed to EPYC.

It would be a good thing if we stop the pretension that EPYC is not selling because Intel is playing dirty and/or doing something illegal. If you have real information that Intel is doing something illegal, I can give you the email of some guy working at AMD for you can give him this information and AMD can go to the court.

EPYC is not selling and customers prefer Intel

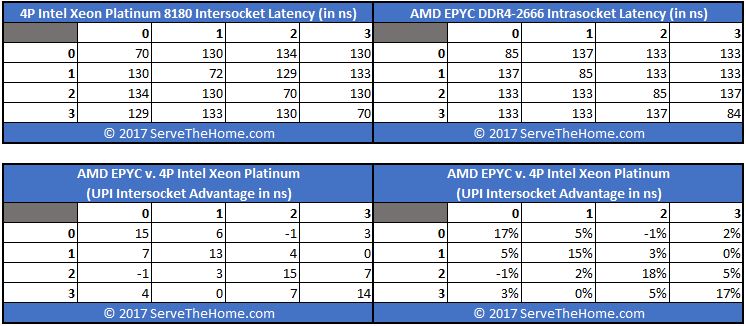

or ARM, because EPYC is not good enough. ServeTheHome just published latency measurements on EPYC vs a 4P Xeon, and found that the intrasocket latencies on EPYC are similar to intersocket latencies on Xeon.

This is a terrible result and everyone that knows those matters is mentioning it. No one is looking to those latency results and saying "Hey look how good those numbers are for EPYC", because they are

not.

In fact some of us predicted

a pair of years ago that the MCM4 approach was going to affect to both latencies and power consumption.

Inefficiences on a MCM approach scale up quadratically with the number of dies: ~O(N^2). The more dies, the worse is the comunication efficiency

Number of dies: Inefficiency

Single die: 0

Dual die: ~1

Quad die: ~

6

It is not fortuitous that 99% of engineers don't use MCM4 for a server CPU, just check the designs by IBM, Sun/Oracle, Fujitsu, Cavium, APM, Intel,... all the engineers chose a monolithic die approach for those server CPUs; no one of those engineers is doing four-die CPUs.