Queuing the salt truck on this one

Rumor: Next-Generation Intel Core i7 To Feature 8 Cores With 12-Core Hyperthreading : Read more

Rumor: Next-Generation Intel Core i7 To Feature 8 Cores With 12-Core Hyperthreading : Read more

Intel would no longer be able to cram 10 cores onto the die as it would grow too big, as even the Core i9 10900K is already at the limits of what the 14nm silicon can do

Well, the die has something like a 2.5:1 aspect ratio, so there certainly is more than enough room to make the die twice as wide under the square IHS. Power delivery for such a doubled-up monstrosity on the other hand could definitely be an issue and require a few hundred more Vcore+ground pins. Most of the extra pins on LGA1200 are for PCIe 4.0 support and to implement the 4.0x4 NVMe interface, not much extra power to be had there.it is not a limit , it is just marketing . and please dont bring on the socket size , because, one : this is just your guessing and nothing official from intel papers.

really ? last time I checked 14nm can do alot , intel already has 18 cores HEDT CPU using that process...

Well, if Intel is going big.LITTLE, it wouldn't be surprising if the big cores were full-blown ones with SMT and the little ones were Atom-like without it to save space and power.

Alder Lake will be the Big Little thing - the 8C 12T is for Rocket Lake and is a typo in the leaked photosWell, if Intel is going big.LITTLE, it wouldn't be surprising if the big cores were full-blown ones with SMT and the little ones were Atom-like without it to save space and power.

Intel has 28C 14nm CPUs...really ? last time I checked 14nm can do alot , intel already has 18 cores HEDT CPU using that process...

it is not a limit , it is just marketing . and please dont bring on the socket size , because,

one : this is just your guessing and nothing official from intel papers.

and two : you are not a CPU designer you are just a writer .

thanks , waiting for more "tomshardware going down" articles

Most likely a typoQueuing the salt truck on this one

Rumor: Next-Generation Intel Core i7 To Feature 8 Cores With 12-Core Hyperthreading : Read more

While SMT on low-power cores may be ideal for highest efficiency, SMT on the fast cores is ideal for peak throughput. It is extremely unlikely that the minimal boost gains (at stupid power cost) you might get from removing SMT would offset the 30-40% throughput loss. And at only ~5% silicon and power cost, SMT is far more power- and silicon- efficient than high-efficiency cores too.The other way around seems more sensible. Pipeline stalls are more likely to occur in the small cores due to smaller caches and weaker branch prediction. Disabling SMT in the big cores could meanwhile allow for higher boost frequency.

Well, if Intel is going big.LITTLE, it wouldn't be surprising if the big cores were full-blown ones with SMT and the little ones were Atom-like without it to save space and power.

HEDT CPU's don't have an IGP like desktop chips do.

Well, it was apparently a typo in this case. Alder Lake is where the big.LITTLE party is starting.Surely if they were going to do that there'd be mention of it. And it also raises--not begs--the question of why only the i7 would be big.LITTLE.

While SMT on low-power cores may be ideal for highest efficiency, SMT on the fast cores is ideal for peak throughput. It is extremely unlikely that the minimal boost gains (at stupid power cost) you might get from removing SMT would offset the 30-40% throughput loss. And at only ~5% silicon and power cost, SMT is far more power- and silicon- efficient than high-efficiency cores too.

If the contest is between full-blown Ice Lake cores with SMT to feed its 10-wide execution back-end and twice as many non-SMT Atom cores with only three execution units, I think it is a pretty safe bet Atom will get its ass served to itself on a silver platter.I'm not convinced that 8 virtual cores would beat 4 physical cores in computational intensive tasks.

Rocket Lake isn't using Skylake cores. We're not sure exactly what it is using, but even if they only move to Sunny Cove, it will have 38% more transistors than Sky Lake. Increase transistor count by at least 38% per core and add an IGP, and the 18 core HEDT becomes irrelevant as a measuring stick.Still, compare the size & shape of the 18-core HEDT dies to even the 10-core Comet Lake. Lots of room to expand horizontally.

LOL - You really don't know how the stock market works, do you? Nvidia has a 78x p/e ratio (undoubtedly due to the Ampere and Ampere GeForce launches) and Intel has a 10.92x. So, yes with that high P/E Nvidia has a higher market cap that Intel ATM. Q22020 Revenues at Intel are $18.5B - which is almost 2x the revenue for Nvidia for an entire year.8 Cores after 2020?

Pathetic.

This is why Nvidia is worth more than Intel.

If the contest is between full-blown Ice Lake cores with SMT to feed its 10-wide execution back-end and twice as many non-SMT Atom cores with only three execution units, I think it is a pretty safe bet Atom will get its ass served to itself on a silver platter.

Most desktop applications are bound by single-threaded performance - finishing individual critical tasks as fast as possible and the cheapest way of giving more things a chance of completing as fast as possible is SMT on very fast cores.If you win a contest and nobody notices, did you really win a contest? The whole idea behind a hybrid architecture is that oftentimes finishing a task quicker is not worth the energy cost.

Sunny Cove has 18% higher IPC on average than Skylake. Willow cove will have at least 10% IPC improvement on top of that so Willow Cove should have around 30% higher IPC on average compared to Skylake. On pure-throughput applications such as tile-based rendering the increase will be closer to 40%. That should correlate with the increase in transistor count. So, per core, Willow cove full-blown cores should feature around 40% more transistors than Skylake-S cores. So 10 cores of Rocketlake-S should roughly take the same die area as 14 Skylake S cores. A Skylake i-gpu, in terms of die area is the same as 2 Skylake S cores. The Tigerlake igpu will probably be the same size as 4 Skylake cores. So a 10-core Rocketlake-S CPU will roughly take a total area equivalent to 18 Skylake S cores (14 Skylake cores for core logic + 4 Skylake S cores for the igpu). PCIe 4 will at worst take as much area as twice the PCIe3 lanes – so for 16PCIe4 lanes+8PCIe3 lanes will take the same area as 40PCIe3 lanes.Rocket Lake isn't using Skylake cores. We're not sure exactly what it is using, but even if they only move to Sunny Cove, it will have 38% more transistors than Sky Lake. Increase transistor count by at least 38% per core and add an IGP, and the 18 core HEDT becomes irrelevant as a measuring stick.

Rocket Lake isn't using Skylake cores. We're not sure exactly what it is using, but even if they only move to Sunny Cove, it will have 38% more transistors than Sky Lake. Increase transistor count by at least 38% per core and add an IGP, and the 18 core HEDT becomes irrelevant as a measuring stick.

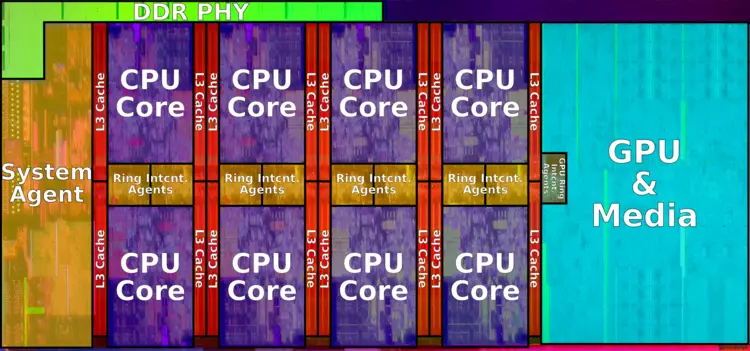

Sure, but look at various chip pictures, and physical sizes. I'm just saying I bet it's possible.

If Intel really wanted to, I'm sure it could make the die square-er by re-arranging the IGP such as moving the IGP to the bottom edge and integrating its ring agent into the system agent (effectively giving the IGP its own single-stop ring) instead of dangling off the CPU ring.There is a reason that mainstream CPU's are rectangular. They can't just fill in the square.