7nm process is essential for semi industry: Q&A with Globalfoundries CTO Gary Patton

Josephine Lien , Taipei; Steve Shen, DIGITIMES [Monday 7 November 2016]

Gary Patton, a 30-year veteran in the semiconductor industry, joined Globalfoundries as CTO in July 2015. He now shoulders the responsibility of building up the foundry house's 7nm manufacturing technology. Patton's task includes the mapping of a clear-cut development strategy for Globalfoundries following its acquisition of IMB's microelectronics business.

Patton outlined his plans for Globalfoundries, and shared his insights into the future of the semiconductor industry with Digitimes during an exclusive interview recently.

Q: What changes have come to Globalfoundries since its acquisition of IBM's microelectronics unit?

A: I used to serve at IBM for eight years and I assumed the post as chief technology officer at Globalfoundries in July 2015. I felt that our CEO Sanjay Jha had done a lot of changes in the past two and a half years, and with the

adding of IBM's differentiated 45/30/22/14 nm process nodes, we have continued to sharpen our algorithm technologies for use in servers, which is essential to the future development of the semiconductor industry.

I believe that the integration between the two sides will give Globalfoundries a clearer blueprint for technology development.

Judging from the industrial development in the computer, networking and handset sectors, although the market seems to have reached the point of saturation, I think the 5G industry, as well as mobile computing, IoT and automotive electronics will be the growth drivers for the next decade, particularly 5G products and datacenters which need support of high-performance computing. These industries will be the major focus of the semiconductor industry in the future.

Q: Can you talk about the roadmaps for FinFET and FD-SOI technologies, as Globalfoundries seems to have been approaching these two technologies parallelly?

A: Our FinFET process is divided into two generations, including 14 nm and 7 nm. We cooperated with Samsung Electronics in the 14nm process previously, but

we have decided to choose a different approach for the 7nm technology and, additionally, the IBM deal has significantly enhanced our resources and development capabilities allowing us to develop the 7nm process in-house.

We also have decided to jump from 14nm to 7nm directly, while skipping the 10nm process because we believe that 10nm will help not much to improve power consumption and costs for clients; the 10nm node is more like a semi-generation process, similar to the previous the 20nm technology, which could not meet clients' requirements.

Additionally, we have received feedbacks from a number of clients indicating that they need the 7nm products urgently, and therefore, we decided to inject our technology resources into developing the 7nm process

. I personally will lead the R&D team, which will include the existing staff of 200 from Globalfoundries and another 500 from IBM. The R&D projects will be carried out mainly in Albany, and some of our R&D personnel in Malta will also join the efforts.

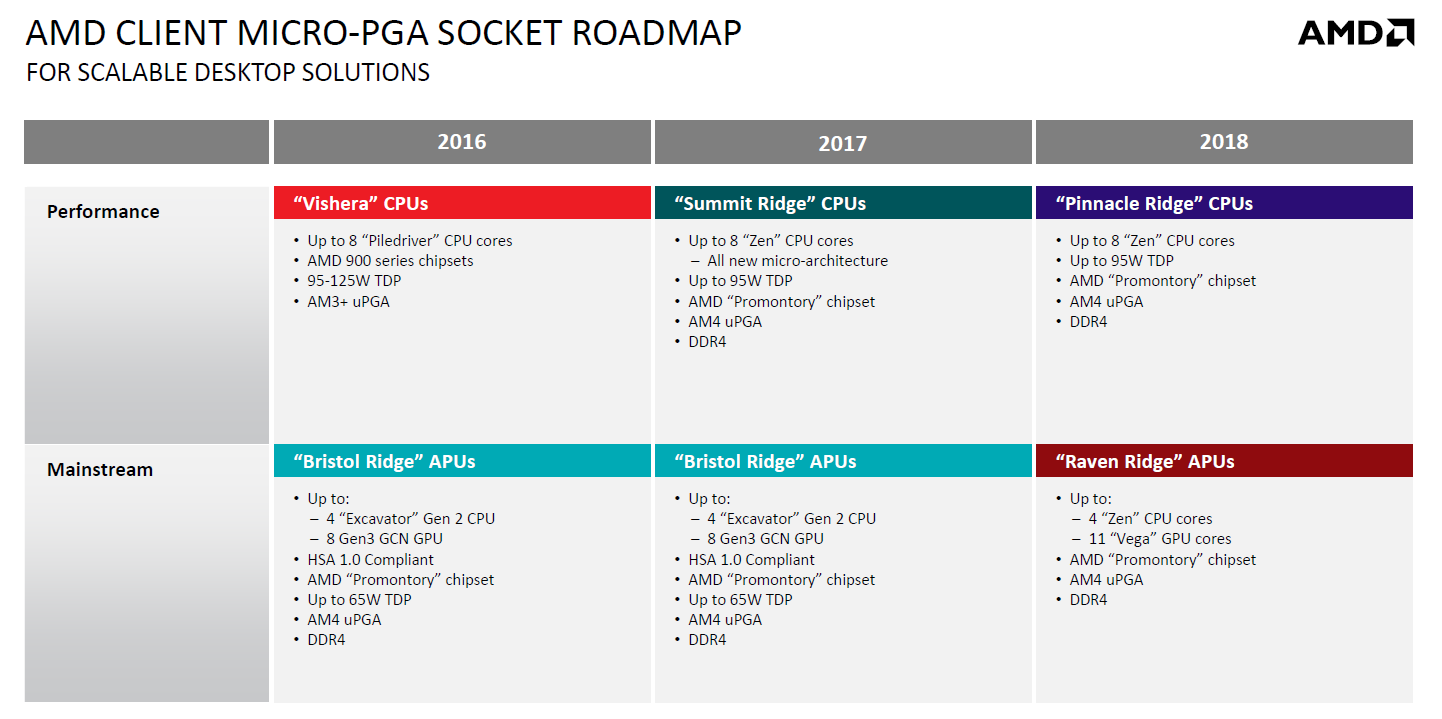

According to our internal roadmap, the 7nm process is expected to enter volume production in the first half of 2018 with initial clients including IBM and AMD. The 7nm process has a number of advantages, including multi-core, high-speed I/O capabilities, reducing power consumption by 60%, upgrading performance by 30%, cutting costs by 30%, doubling the yield rate per wafer, while providing 2.5D/3D packaging services.

Q:

Why is there no plan to introduce extreme-ultraviolet (EUV) technology at the 7nm process?

A: The EUV technology is expected to become mature in 2019, but our major clients need the 7nm products to be in mass production in early 2018.Therefore we still continue to use the current optical technology, instead of using the EUV technology.

Samsung's decision to introduce in advance the EUV technology into its 7nm process means that Globalfoundries and Samsung are approaching different technologies for the development of the 7nm node. But we do not know the situations at the Korea company.

Q: What is your intention to develop FD-SOI technology in addition to FinFET process?

A: FinFET is a very good technology but also relatively complex and costly because it needs two to four more extra steps in the multiple-exposure process. But some clients do not need products in such a performance level; particularly some small and medium IC design houses cannot afford the mask development cost for the FinFET process. For clients, mostly IoT device vendors, who are cost sensitive but also want to achieve a balance in performance, then the FD-SOI technology will be the most appropriate choice for them.

We already have two generations of roadmap for the FD-SOI technology, with the first one being the 22FDX; its process design kit (PDK) 0.5 version was completed in the second quarter of 2016 and we have already approached 50 potential clients. The 22FDX process is expected to begin risk trial production in the fourth quarter of 2016 and enter volume production in the first quarter of 2017.

The performance of the 22FDX chips is comparable to that of 28 nm products, but its power consumption is 70% less than that of the 28nm HKMG process. Additionally, a single 22FDX chip can be integrated with RF functionality. These features make the 22FDX process ideal for IoT devices.

Furthermore, the 22FDX process will be incorporated with the embedded MRAM technology from the memory provider Everspin Technologies; the reason to adopt the embedded MRAM technology at the 22nm process is because the embedded flash technology will encounter some bottlenecks from the 28 nm process onwards. We will also use the embedded MRAM technology in the FinFET process and also the 12FD-SOI process.

In addition, we have also begun to develop the second generation FD-SOI technology, namely 12FDX, which is scheduled to enter commercial production in 2019. This roadmap clearly indicates that we are picking up the 22/12 nm FD-SOI processes rather than the 20/10 nm ones, simply to reduce the mask exposure cost.

The 12FDX chips can reduce power consumption by 50% as compared to 16/14 nm FinFET chips and lower the mask cost by 40% as compared to 10nm FinFET process.

Our IC-designing clients in China are keen to adopt the FD-SOI technology, and we believe that Globalfoundries will be the core supplier of the FD-SOI technology in the global market in the future.

Q: Can you talk about your ecosystem which is similar to that the OIP (Open Innovation Platform) of TSMC?

A: Our ecosystem is called FDXcelerator, which is designed to shorten the time to market for products and our partners in the system include Cadence, Synaptics, Verisilicon, Invecas, Encore Semi, among others.

Q: How do you view the competition with rival companies including TSMC, Samsung and Intel?

A: As the global semiconductor industry moves into the 7nm process, there are only four companies that can offer related products, Globalfoundries, TSMC, Samsung and Intel, of which two are pure-play foundries. We value much the 7nm process believing that this process will be a very important and long-living technology for the semiconductor industry;

we have already secured a number of clients and we have great confidence in the 7nm process race.

This was November 7th 2016, and is still inline with most recent statements GlobalFoundries has made with it's projections of it's internal road map for 7nm, and an addition of extra performance beyond the 30% noted. This isn't the same old GlobalFoundries after the acquisition of IBM's microelectronics unit.

http://www.digitimes.com/news/a20161102PD203.html