New 12LP technology offers density and performance improvement over current generation

Platform features enhancements for next-gen automotive electronics and RF/analog applications

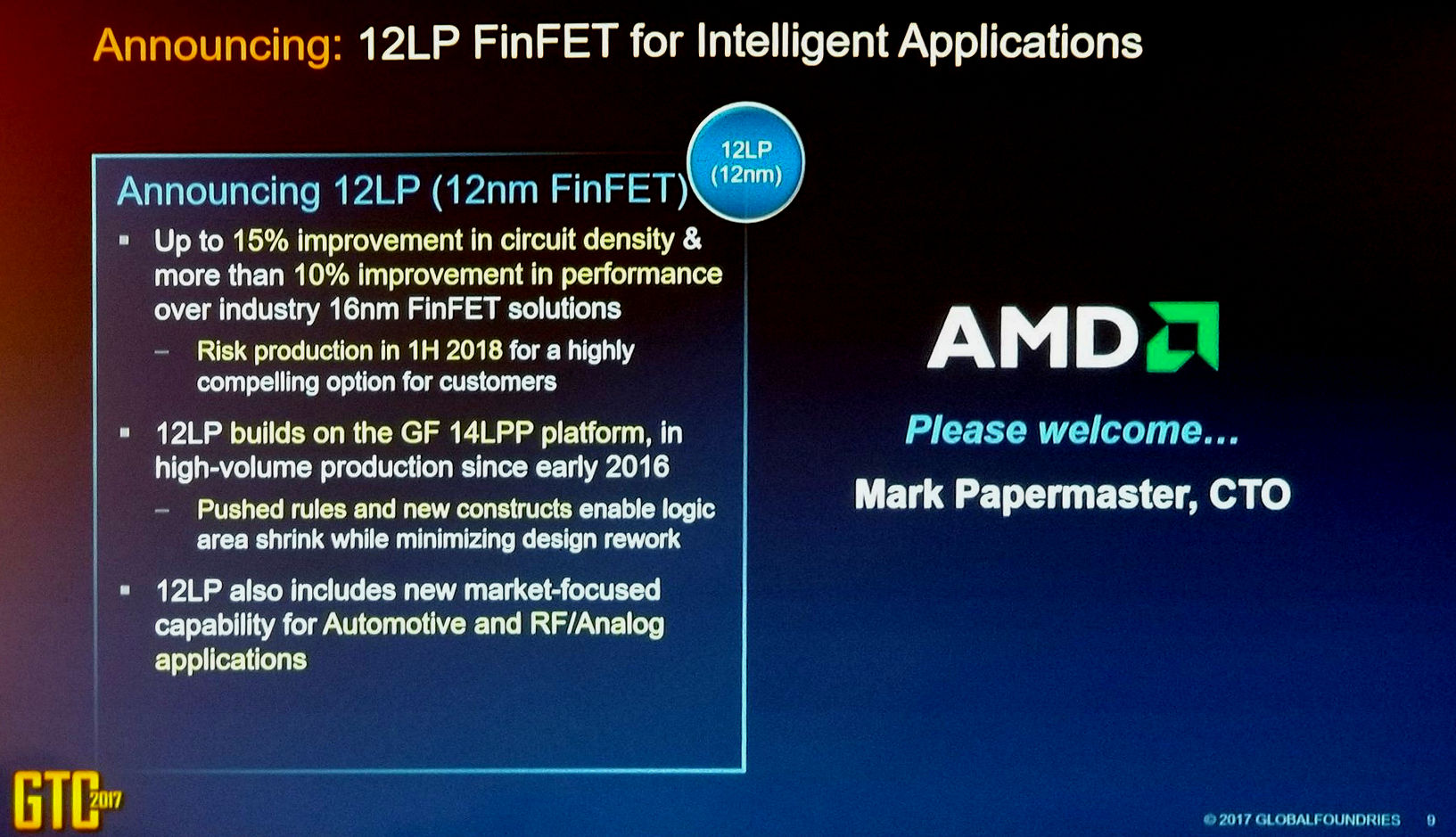

Santa Clara, Calif., Sept. 20, 2017 – GLOBALFOUNDRIES today announced plans to introduce a new 12nm Leading-Performance (12LP) FinFET semiconductor manufacturing process. The technology is expected to deliver better density and a performance boost over GF’s current-generation 14nm FinFET offering, satisfying the processing needs of the most demanding compute-intensive applications from artificial intelligence and virtual reality to high-end smartphones and networking infrastructure.

The new 12LP technology provides as much as a 15 percent improvement in circuit density and more than a 10 percent improvement in performance over 16/14nm FinFET solutions on the market today. This positions 12LP to be fully competitive with other 12nm FinFET foundry offerings. The technology leverages GF's expertise at Fab 8 in Saratoga County, N.Y., where its 14nm FinFET platform has been in high-volume production since early 2016.

“The world is in the midst of an unprecedented transition to an era of connected intelligence,” said GF CEO Sanjay Jha. “This new 12LP technology provides the performance and density improvements necessary to help our customers continue innovating at the system level, as they deliver real-time connectivity and edge processing to everything from high-end graphics and automobiles to industrial applications.”

“We are pleased to extend our longstanding relationship with GLOBALFOUNDRIES as a lead customer for their new 12LP technology,” said Mark Papermaster, CTO and senior vice president of technology and engineering, AMD. “Our deep collaboration with GF has helped AMD bring a set of leadership high-performance products to market in 2017 using 14nm FinFET technology. We plan to introduce new client and graphics products based on GF’s 12nm process technology in 2018 as a part of our focus on accelerating our product and technology momentum.”

In addition to transistor-level enhancements, the 12LP platform will include new market-focused features specifically designed for automotive electronics and RF/analog applications—two of the fastest-growing segments in the industry.

Emerging automotive applications in vehicle safety and automated driving require a combination of processing power and extreme reliability. The 12LP platform delivers both, with plans for Automotive Grade 2 qualification at Fab 8 by Q4 2017.

A new RF offering extends the 12LP platform for RF/analog applications such as premium-tier transceivers in sub-6GHz wireless networks. 12LP offers the best scaling in both logic and memory for RF chip architectures with primarily digital and less RF/analog content.

GF's new 12nm FinFET technology complements its existing 12nm FD-SOI offering, 12FDXTM. While some applications require the unsurpassed performance of FinFET transistors, many connected devices need high levels of integration and more flexibility for performance and power consumption, at costs FinFET cannot achieve. 12FDX provides an alternative path for the next generation of connected intelligent systems, enabling the performance of 10nm FinFET with better power consumption, lower cost, and better RF integration than current-generation foundry FinFET offerings.